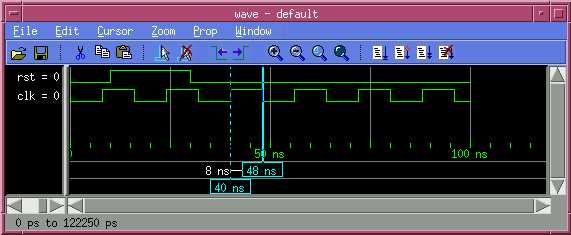

Practically every testbench needs a clock and a reset signal. This section shows a simple way to implement them:

. . .

signal clk: std_logic := '0';

signal rst: std_logic;

begin

rst <= '0', '1' after 10 ns, '0' after 30 ns;

clk <= not clk after 8 ns;

. . .

Note that the clk signal needs to be initialized in the declaration, as the inverse

of 'U' (=uninitialized) is also 'U'. Here is the simulation result:

Below are the files which have been simulated in this section:

|

| tb_clk_rst.vhd |